Toto je jednoduchá diagnostická ("POST" - Power On Self Test) 8-bitová ISA karta pro diagnostiku starých základních desek s ISA sloty. Během POSTu (samo-test, který provádí BIOS spolu s inicializací komponent po zapnutí počítače) BIOS posílá na I/O port 80h diagnostické kódy. Na této diagnostické kartě je 2-místný, 7-segmentový displej, který zobrazuje v hexadecimální podobě poslední kód poslaný na port 80h. V případě, že počítač odmítá startovat a ani se neprovede inicializace grafické karty, a tudíž se nezobrazí na monitoru žádné diagnostické informace, je diagnostická karta užitečný nástroj, protože hexadecimální diagnostické kódy mají podstatně větší výpovědní hodnotu oproti zvukovým, "pípaným" kódům. Jedná se o vhodnou pomůcku pro opravu "historických" (<2000) desek.

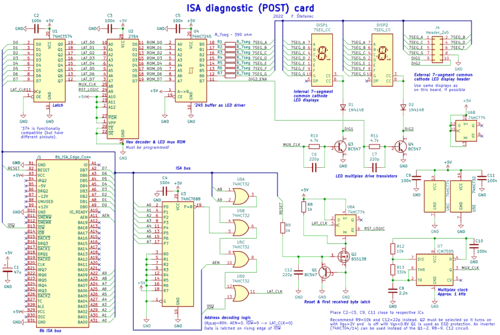

Schéma zapojení (klikněte pro plné rozlišení)

Tato karta pro své napájení používá pouze +5V větev. Je možné použít HCT, LS či ALS logiku. Integrovaný obvod U3 (74HCT688 - equality komparátor) dekóduje spodních osm adresních linek a přepne výstup do logické 0, pokud A[7:0]=80h. OR logická hradla (U5) jsou použita pro dekódování adresních linek A8, A9 (tato karta dekóduje pouze spodních 10 adresních linek), AEN (DMA vs CPU) a ~IOW (příkaz pro I/O zápis, aktivní v log. 0). Karta naslouchá na portu 80h. Pokud A[9:0]=80h, AEN=0 (sběrnici řídí CPU, ne DMA) a ~IOW=0 (probíhá I/O zápis), tak dojde ke stažení uzlu LAT_CLK na log. 0, jinak je uzel LAT_CLK v log. 1. Jakmile je během sekvence zápisu deaktivován signál ~IOW (přejde do log. 1), zatímco na sběrnici jsou ještě validní data (D[7:0]), LAT_CLK také přejde z log. 0 do 1. U1 (74HCT574 či '374 - jiné zapojení pinů, stejná funkce) data uloží na náběžné hraně LAT_CLK.

Při resetu systému dojde k resetu U6A (1/2 74HCT74) - invertovaný výstup (vedoucí na uzel RST_LOGIC) přejde do log. 1. Jakákoliv náběžná hrana LAT_CLK (tzn. jakákoliv data poslaná na port 80h) překlopí U6A a uzel RST_LOGIC se přepne do logické 0. Protože resetovací vstupy 74HCT74 jsou aktivní v log. 0, RESET signál z ISA sběrnice je invertován pomocí obvodu s tranzistorem Q2.

Přijatý hexadecimální kód je zobrazen na displeji skládajícím se ze dvou multiplexovaných 7-segmentových zobrazovačů se společnou katodou. Taktovací signál pro multiplex je získán pomocí integrovaného obvodu U7 (časovač 555, může být jak klasický, tak CMOS) a má frekvenci přibližně 1 kHz. Anody displeje jsou buzeny pomocí bufferu 74HCT245 (U4), katody jsou buzeny pomocí tranzistorů Q3 a Q4, jejichž vypínání je zrychleno pomocí kondenzátorů C6 a C7. Strany A a B bufferu '245 lze přehodit, pokud se pin 1 připojí na GND místo +5 V. Dekódování hexadecimálních dat pro 7-segmentový displej a řízení multiplexu zajišťuje ROM typu 2764 (U2, 27C64 - lze použít například NMC27C64Q či podobnou), případně 27C256 (pokud je pin 26 připojen k +5V nebo GND). ROM je naprogramovaná tak, aby na pinu D7 byla obrácená log. úroveň oproti pinu A8 (MUX_CLK) pro řízení katody druhého zobrazovače, a aby na pinech D0-D6 byly úrovně pro řízení segmentů (A-G) odpovídající hexadecimální hodnotě buď adresních linek ROM A[7:4] (první zobrazovač - pokud je MUX_CLK v log. 1) či A[3:0] (druhý zobrazovač, MUX_CLK=0). Pokud je uzel RST_LOGIC, tedy i pin ROM A9 v log. 1, na displeji je zobrazeno pouze "--" jako signalizace, že po resetu zatím nebyl přijat žádný kód.

V sérii s katodami zobrazovačů jsou zapojeny diody 1N4148 - pokud na konektor J4 budou připojeny stejné či podobné sedmisegmentovky, tak díky úbytku diod (cca 0,7 V) na zabudované zobrazovače nezbyde dostatečné napětí a budou v provozu pouze externí sedmisegmentovky. Kondenzátory C2-C5, C9-C11 by měly být umístěny blízko příslušných integrovaných obvodů. Pro ochranu citlivého MOSFETu BSS138 je zde použit B-E přechod tranzistoru BC547 jako nízkokapacitní Zenerova dioda (Q1 musí být umístěn blízko Q2). Bylo by možné, a i vhodnější, použít jeden invertor z obvodu 74HCT04 či '14 místo tohoto diskrétního obvodu. Pokud nevadí u RESETu zpoždění okolo ~1 ms pro zaznamenání přechodu RESETu ISA sběrnice do log. 1 (pravděpodobně nevadí), lze použít klopný obvod U6B (připojit ~S a D na +5V, ~R na RESET linku sběrnice, vstup C na MUX_CLK, výstup Q nechat nezapojen, výstup ~Q připojen na ~R vstup Q6A - v tomto případě, stejně jako s invertorem '04/'14, součástky R8-9, C12, Q1-2 zůstanou neosazeny).

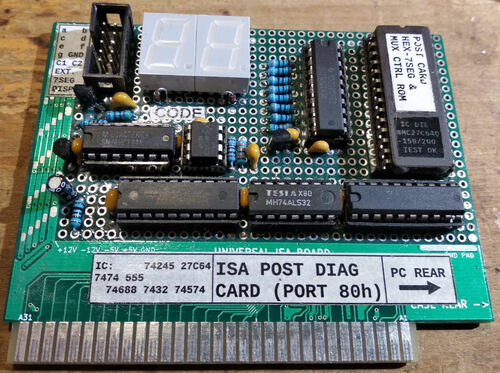

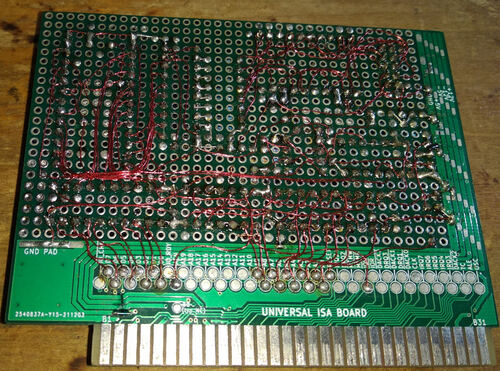

Tento obvod byl sestaven na univerzální ISA kartě s pomocí pájitelného lakovaného drátu. Byly použity převážně THT komponenty. Na ochranu desky byl použit lak z šelaku s příměsí kalafuny.

ROM je nutné pro správnou funkci naprogramovat. Já jsem použil programátor TL866II+. Binární soubory jsou dostupné ke stažení na konci stránky. Z ROM je využit pouze 1 kB (prvních 10 adresních linek - data se poté opakují) a obvod je možné upravit i pro jiné typy ROM.

Prototyp, vrchní strana (klikněte pro plné rozlišení)

Prototyp, spodní strana (klikněte pro plné rozlišení)

Pin 8 integrovaného obvodu U7 (ICM7555) spolu se součástkami C10, R12 by měl být připojen k +5V větvi, ale ve schématu toto propojení chybí. Bez něj nebude displej pracovat správně.